【产学研视点】集成电路学科:从基础到前沿的硬核科普

集成电路是信息技术的核心,被称为“现代工业的粮食”。集成电路学科则是支撑这一核心的基础学科,融合多领域知识,贯穿设计、制造、封装测试全链条。理解这一学科,就能把握信息技术发展的底层逻辑。

1.1 学科定义与核心范畴

集成电路学科以半导体为核心载体,研究电子器件、电路系统的设计、制造及应用。核心范畴包括半导体材料特性、器件物理结构、电路设计原理、制造工艺技术、封装测试方法,以及系统集成与应用开发。

这一学科本质是“微型化的电子系统工程”,通过将大量晶体管及电子元件集成在微小芯片上,实现信息的处理、存储与传输。与传统电子学科不同,它更强调“集成”带来的性能提升与成本优化,是多学科交叉的产物。

1.2 学科的核心价值

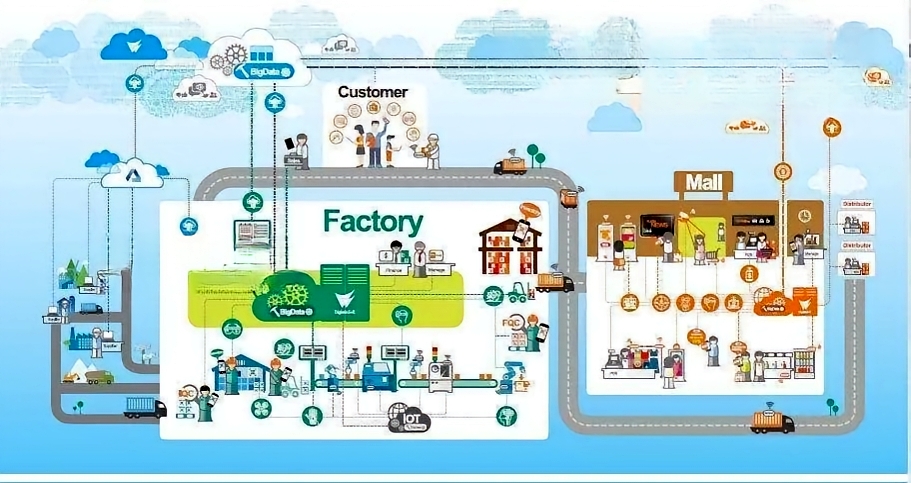

集成电路学科的价值体现在支撑全产业链发展。从手机、电脑等消费电子,到通信基站、工业控制,再到航空航天、人工智能,所有信息技术产品的核心都依赖集成电路。学科的发展直接决定了一个国家信息技术的核心竞争力,是数字经济的基石。

在技术迭代中,集成电路学科不断突破物理极限,推动芯片性能提升。摩尔定律的持续演进,本质上是学科内材料、器件、工艺等领域协同创新的结果。每一次芯片制程的突破,都伴随着学科理论与技术的重大进步。

2.1 半导体基础:学科的物质根基

2.1.1 半导体材料特性

半导体材料是集成电路的载体,核心特性是导电性可调控。纯半导体(本征半导体)导电性差,通过掺杂形成N型(含自由电子)和P型(含空穴)半导体,二者结合形成PN结,是二极管、晶体管等器件的核心结构。

主流半导体材料为硅,储量丰富、稳定性高,能适应复杂制造工艺。化合物半导体如砷化镓、氮化镓,在高频、高温、光电领域表现更优,是特殊场景芯片的核心材料。新兴的二维半导体材料如石墨烯、黑磷,有望突破硅基材料的物理极限,是学科前沿研究方向。

2.1.2 半导体器件物理

半导体器件是集成电路的基本单元,核心是晶体管。晶体管的本质是“电子开关”,通过控制电压或电流,实现电路的通断与信号放大。按结构分为双极型晶体管(BJT)和场效应晶体管(FET),当前集成电路中以金属-氧化物-半导体场效应晶体管(MOSFET)为主。

MOSFET的核心结构包括栅极、源极、漏极和衬底。栅极通过电场控制沟道形成,进而调控源漏极之间的电流。随着制程缩小,栅极绝缘层厚度已达纳米级,量子隧穿效应凸显,学科通过引入高k介质、金属栅极等技术解决这一问题。

2.2 集成电路设计:从功能到电路的转化

2.2.1 设计流程与层级

集成电路设计是将系统功能转化为物理电路的过程,按层级分为系统级设计、算法级设计、RTL级设计、门级设计、晶体管级设计。系统级明确芯片功能与性能指标,算法级将功能拆解为数学算法,RTL级用硬件描述语言(Verilog/VHDL)描述电路逻辑,门级进行逻辑综合,晶体管级完成物理实现。

设计流程遵循“自顶向下”与“自底向上”结合的模式。自顶向下完成功能拆解与逻辑设计,自底向上进行单元库开发与验证。验证是设计的核心环节,包括功能验证、时序验证、功耗验证,确保芯片满足设计需求。

2.2.2 数字集成电路设计

数字集成电路处理离散信号,核心是逻辑电路。基本逻辑单元包括与门、或门、非门等,通过组合形成加法器、乘法器、寄存器、控制器等模块。数字电路设计的关键是时序优化与功耗控制,时序决定芯片运行速度,功耗影响续航与可靠性。

同步数字电路是主流,采用时钟信号同步各模块工作。时钟树设计直接影响时序性能,需保证时钟信号到达各单元的延迟一致(时钟 skew控制)。随着芯片规模扩大,异步数字电路因低功耗、高速度特性,成为前沿研究方向,其无需全局时钟,通过握手信号实现模块协同。

2.2.3 模拟集成电路设计

模拟集成电路处理连续信号,如电压、电流,核心是放大、滤波、转换等功能。主要模块包括运算放大器、比较器、电源管理芯片、模数/数模转换器(ADC/DAC)。模拟电路设计对器件特性依赖性强,需解决噪声、失真、温度漂移等问题。

运算放大器是模拟电路的核心单元,追求高增益、宽带宽、低噪声。ADC/DAC是连接模拟与数字世界的桥梁,ADC将模拟信号转化为数字信号,DAC则相反,其精度与速度直接决定混合信号系统的性能。

2.2.4 射频集成电路设计

射频集成电路工作于高频波段(通常>300MHz),用于无线通信中的信号收发。核心模块包括天线、功率放大器、低噪声放大器、混频器、振荡器。射频电路设计需解决阻抗匹配、电磁干扰、非线性失真等问题,对器件高频特性要求极高。

功率放大器负责信号放大,需平衡输出功率与效率;低噪声放大器用于接收端,减少噪声引入;混频器实现信号频率转换,是射频前端的核心。随着5G、卫星通信发展,射频集成电路向高频、宽带、低功耗方向演进。

2.3 集成电路制造:从版图到芯片的实现

2.3.1 制造流程核心环节

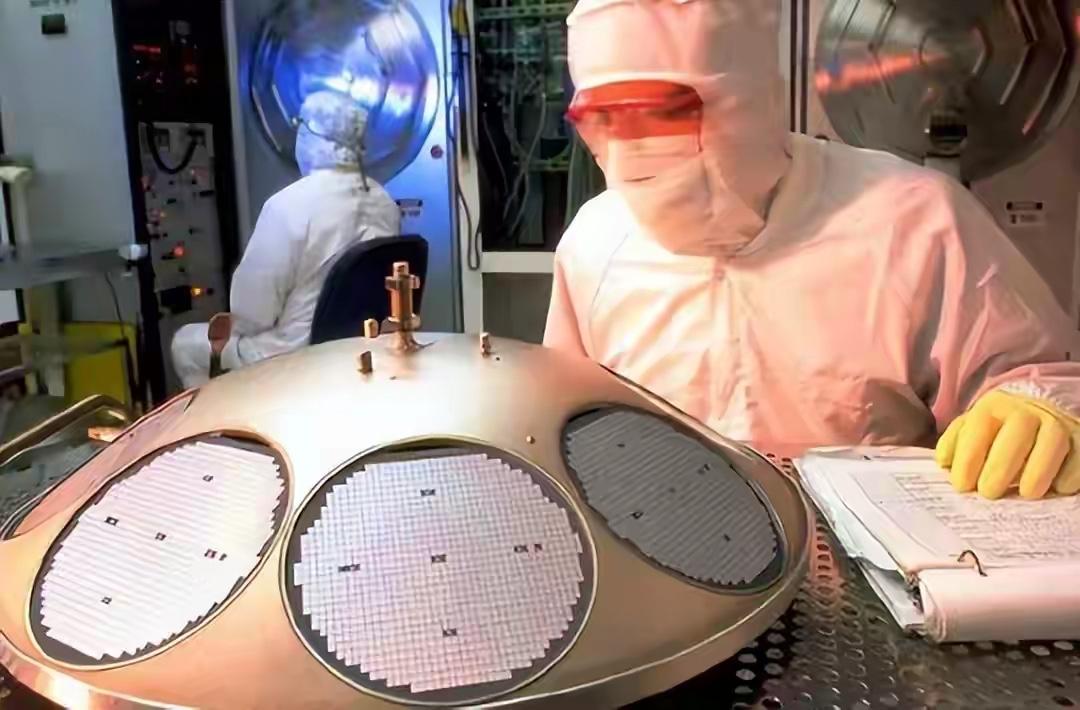

集成电路制造是将设计版图转化为物理芯片的过程,核心流程包括晶圆制备、光刻、刻蚀、掺杂、薄膜沉积、抛光等。晶圆制备是基础,通过拉晶、切片、抛光等工艺,制成高纯度、低缺陷的硅晶圆;光刻是“绘图”,通过光刻胶与光刻机,将版图图案转移到晶圆表面;刻蚀是“雕刻”,按光刻图案去除多余材料;掺杂通过离子注入或扩散,改变半导体导电特性;薄膜沉积用于形成金属导线与绝缘层;抛光则提升晶圆表面平整度。

制造流程需重复数十次,每次都需严格控制精度与缺陷。7nm制程下,光刻精度已达纳米级,任何微小杂质或误差都可能导致芯片失效。洁净室是制造的关键环境,空气中的尘埃颗粒直径需控制在0.1微米以下。

2.3.2 关键制造技术

光刻机是制造的核心设备,决定制程极限。深紫外光刻(DUV)通过多重曝光技术,实现7nm制程;极紫外光刻(EUV)采用13.5nm波长光源,直接支持5nm及以下制程,是先进工艺的核心。EUV技术集成了精密光学、机械与真空技术,制造难度极高。

铜互连技术替代铝互连,是制造技术的重大突破。铜的导电性优于铝,可降低导线电阻与功耗。化学机械抛光(CMP)技术则保障了铜互连的表面平整度,实现多层导线的叠加。三维晶体管结构(如FinFET)通过提升栅极控制能力,解决了平面晶体管的漏电问题,支撑了14nm及以下制程的发展。

2.4 集成电路封装测试:芯片的“外衣”与“质检”

2.4.1 封装技术

封装是为芯片提供机械保护、电气连接与散热通道的过程。核心功能包括:保护芯片免受环境影响,实现芯片与外部电路的信号传输,导出芯片工作时产生的热量。封装技术按结构分为DIP(双列直插)、SOP(小外形封装)、QFP(四方扁平封装)、BGA(球栅阵列封装)、CSP(芯片级封装)等。

先进封装技术是当前发展热点,包括倒装芯片(Flip Chip)、晶圆级封装(WLP)、系统级封装(SiP)、 Chiplet(芯粒)技术。Chiplet将大芯片拆解为多个小芯粒,通过先进封装集成,可突破单芯片制造极限,提升良率与性能。

2.4.2 测试技术

测试是确保芯片质量的核心环节,贯穿设计与制造全流程。按阶段分为设计验证、晶圆测试(中测)、成品测试(终测)。设计验证通过仿真与原型验证,确保设计方案可行;晶圆测试在制造完成后,检测晶圆上的坏片,减少后续成本;成品测试检查封装后的芯片性能,筛选合格产品。

测试技术依赖测试设备(ATE)与测试向量。ATE提供输入信号并采集输出信号,与标准结果对比判断芯片是否合格。测试向量需覆盖芯片所有功能点,确保无测试盲区。随着芯片复杂度提升,测试成本占比已达芯片总成本的30%以上,降低测试成本是学科研究方向之一。

3.1 EDA工具:设计的“智能画笔”

EDA(电子设计自动化)工具是集成电路设计的核心支撑,涵盖设计、仿真、验证、制造全流程。核心工具包括逻辑综合工具、布局布线工具、仿真工具、时序分析工具、物理验证工具。EDA工具将复杂的设计流程自动化,大幅提升设计效率,降低出错概率。

逻辑综合工具将RTL代码转化为门级网表;布局布线工具完成单元摆放与导线连接,优化时序与面积;仿真工具模拟芯片工作状态,验证功能正确性;时序分析工具检查电路是否满足速度要求;物理验证工具确保设计版图符合制造规则。

EDA行业技术壁垒极高,需融合集成电路设计、制造工艺、计算机算法等多领域知识。先进制程的EDA工具开发成本达数十亿美元,全球仅有少数企业具备全流程工具开发能力。

3.2 半导体设备与材料:制造的“基石”

3.2.1 半导体设备

半导体设备是制造的核心保障,按工艺分为光刻设备、刻蚀设备、离子注入设备、薄膜沉积设备、抛光设备等。光刻设备占设备投资的30%以上,是最关键的设备;刻蚀设备用于图案转移,精度直接影响芯片性能;离子注入设备实现精确掺杂,决定器件导电特性。

半导体设备技术迭代快,与制程节点同步发展。7nm制程需用到EUV光刻设备、原子层刻蚀设备等;5nm及以下制程,设备需突破更高精度与控制能力。设备制造涉及精密机械、光学、真空、自动化等多领域技术,是衡量国家制造业水平的重要标志。

3.2.2 半导体材料

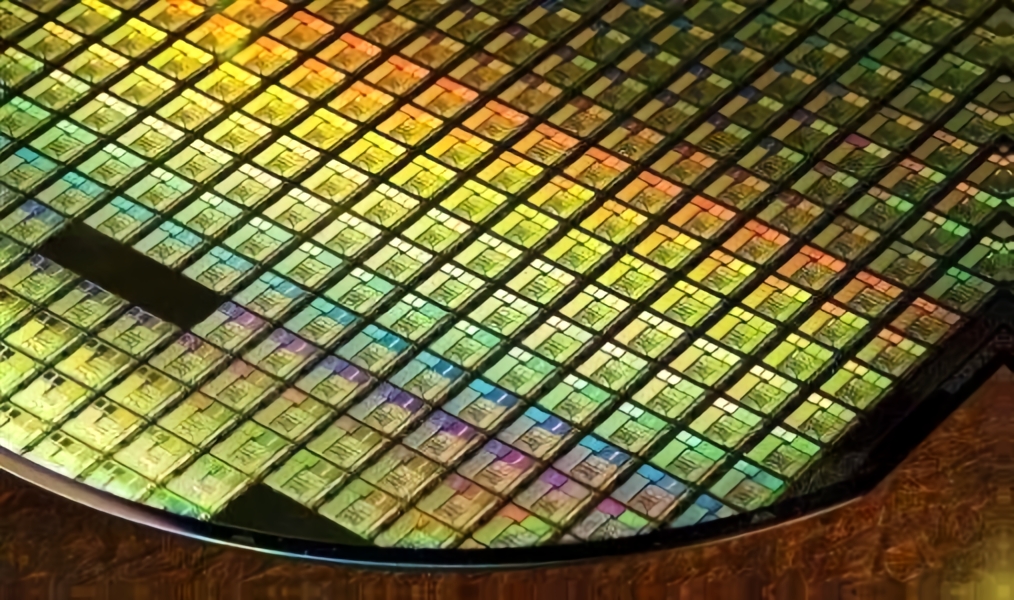

半导体材料包括晶圆衬底、光刻胶、靶材、特种气体、湿电子化学品、封装材料等。晶圆衬底是芯片的载体,占材料成本的40%左右;光刻胶是光刻工艺的核心材料,需具备高分辨率与稳定性;靶材用于薄膜沉积,纯度要求达99.999%以上;特种气体用于掺杂与刻蚀,纯度与稳定性直接影响工艺质量。

半导体材料对纯度、均匀性要求极高。先进制程下,材料的微小缺陷都可能导致芯片失效。例如,12英寸硅晶圆的直径误差需控制在微米级,光刻胶的颗粒尺寸需小于1nm。材料技术的突破往往是制程升级的前提。

3.3 可靠性与失效分析:芯片的“健康保障”

可靠性是集成电路的核心指标,指芯片在规定条件下长期稳定工作的能力。失效分析则是研究芯片失效原因的技术,为可靠性提升提供依据。可靠性问题包括热失效、电迁移失效、时间相关介质击穿(TDDB)、负偏压温度不稳定性(NBTI)等。

热失效是最常见的问题,芯片工作时产生的热量若无法及时导出,会导致性能下降甚至烧毁。通过热设计优化封装结构、采用高导热材料,可提升散热能力。电迁移是金属导线中电子撞击原子导致的导线失效,通过选用高熔点金属、优化导线宽度,可延长使用寿命。

失效分析技术包括物理失效分析与电性失效分析。物理失效分析通过切片、扫描电镜(SEM)、透射电镜(TEM)等手段,观察芯片内部结构缺陷;电性失效分析通过测试电学参数,定位失效节点。失效分析是连接设计与制造的桥梁,可指导设计优化与工艺改进。

4.1 消费电子领域

消费电子是集成电路最主要的应用领域,包括手机、电脑、平板、智能穿戴等。手机中的处理器(CPU)、图形处理器(GPU)、基带芯片、存储芯片,电脑中的主板芯片组、内存芯片,智能穿戴中的传感器芯片,均为集成电路学科的产物。

消费电子对芯片的需求集中在高性能、低功耗、小尺寸。手机处理器从单核发展到多核,制程从28nm升级至3nm,性能提升数十倍,功耗却大幅降低。存储芯片容量不断突破,1TB级手机存储已成为主流,这依赖于存储电路设计与制造工艺的进步。

4.2 通信领域

通信领域的发展离不开集成电路的支撑,从2G到5G,每一代通信技术的升级都伴随芯片技术的突破。基站中的射频芯片、信号处理芯片,手机中的基带芯片,光通信中的光模块芯片,是通信系统的核心。

5G通信对芯片提出更高要求,毫米波通信需要高频射频芯片,Massive MIMO技术需要多通道信号处理芯片。卫星通信则需要抗辐射、高可靠性的芯片,以适应太空恶劣环境。集成电路学科为通信技术的迭代提供了核心动力。

4.3 汽车电子领域

汽车电子是集成电路的新兴增长点,智能网联汽车的发展推动芯片需求爆发。汽车芯片包括动力控制芯片、车身控制芯片、车载娱乐芯片、自动驾驶芯片、传感器芯片等。一辆传统汽车需数百颗芯片,智能汽车则需数千颗。

自动驾驶芯片是核心,需具备强大的AI计算能力与实时数据处理能力,以支持环境感知、决策规划等功能。汽车芯片对可靠性与安全性要求极高,需通过严苛的车规认证,工作温度范围、抗振动能力等指标远高于消费电子芯片。

4.4 航空航天与国防领域

航空航天与国防领域对集成电路的需求具有特殊性,强调高可靠性、抗辐射、耐极端环境。卫星、导弹、战斗机中的导航芯片、通信芯片、雷达芯片、制导芯片,均需满足严苛的性能要求。

抗辐射芯片是该领域的核心,太空环境中的高能粒子会导致芯片逻辑错误或永久损坏。通过采用抗辐射设计(如冗余设计)、选用抗辐射材料,可提升芯片的抗辐射能力。国防领域的集成电路还需具备加密功能,确保信息安全。

4.5 人工智能与大数据领域

人工智能与大数据的发展依赖于算力支撑,而算力的核心是AI芯片。AI芯片包括GPU、FPGA、ASIC、类脑芯片等,通过并行计算架构,实现对海量数据的快速处理。深度学习模型的训练与推理,均需AI芯片提供强大的算力支持。

ASIC芯片为特定AI算法定制,算力与能效比优于通用芯片,是当前AI芯片的主流方向。类脑芯片则模仿人类大脑神经元结构,具有低功耗、高容错性的特点,是未来AI芯片的发展方向。集成电路学科通过优化芯片架构与计算模式,持续提升AI算力。

5.1 学科发展历程

5.1.1 初创阶段(1950s-1960s)

1947年晶体管发明,为集成电路奠定基础。1958年,美国德州仪器公司发明第一块集成电路,将多个晶体管集成在单块硅片上,标志着集成电路学科的诞生。这一阶段的芯片制程为毫米级,集成度低,主要用于军事领域。

学科核心任务是验证集成电路的可行性,解决器件集成中的兼容性问题。1965年,摩尔提出摩尔定律,预测晶体管集成度每18-24个月翻一番,成为学科发展的指导规律。

5.1.2 成长阶段(1970s-1990s)

这一阶段,集成电路从军事应用转向民用,消费电子市场的崛起推动学科快速发展。1971年,第一块微处理器诞生,开启了个人计算机时代。制程从微米级向亚微米级演进,集成度从千级提升至百万级。

学科重点转向提升集成度与降低成本,MOSFET技术成为主流,CMOS工艺因低功耗特性逐渐取代NMOS工艺。EDA工具开始出现,推动设计效率提升。1980s,集成电路产业形成设计、制造、封装测试分工模式,产业生态初步建立。

5.1.3 成熟阶段(2000s-2010s)

制程进入纳米级,2004年90nm制程量产,2011年28nm制程成为主流。集成度突破十亿级,芯片性能大幅提升。智能手机的普及推动移动芯片发展,基带芯片、GPU等成为研究热点。

学科面临物理极限挑战,摩尔定律增速放缓。高k金属栅极、FinFET等技术的突破,延续了摩尔定律。先进封装技术开始受到重视,成为提升芯片性能的重要途径。中国、韩国等国家加大对集成电路学科的投入,全球产业格局发生变化。

5.1.4 前沿阶段(2020s至今)

制程进入5nm及以下,EUV光刻技术成为先进工艺的核心。Chiplet技术、异构集成成为学科前沿,通过芯粒组合与不同类型芯片集成,突破单芯片制造极限。AI芯片、汽车芯片、量子芯片成为研究热点,学科应用场景持续拓展。

学科发展呈现“设计-制造-封装”协同创新的特点,同时强调与人工智能、量子信息等前沿学科的交叉融合。各国将集成电路学科提升至战略高度,核心技术自主可控成为重要目标。

5.2 未来发展趋势

5.2.1 制程极限与技术突破

硅基芯片的物理极限逐渐显现,3nm以下制程面临量子隧穿、热效应等问题。学科将通过新材料(如二维半导体、宽禁带半导体)、新器件结构(如叉片晶体管、纳米线晶体管)突破极限。量子点晶体管、单电子晶体管等新型器件的研究,有望开启后摩尔时代。

EUV光刻技术将向更高精度发展,极紫外多重曝光技术可能用于2nm及以下制程。同时,无掩模光刻、电子束光刻等新型光刻技术正在研发,有望降低对EUV设备的依赖。

5.2.2 先进封装与系统集成

先进封装将成为提升芯片性能的核心途径,Chiplet技术将实现“按需集成”,不同功能、不同制程的芯粒通过高速互连集成,提升系统性能与良率。3D封装技术通过芯片堆叠,减少互连延迟,提升集成度。

异构集成将不同类型的芯片(如逻辑芯片、存储芯片、传感器芯片)集成在同一封装内,实现功能融合。系统级封装(SiP)将进一步小型化,满足智能穿戴、物联网等场景的需求。封装互连技术将向高速、低损耗方向发展,如硅通孔(TSV)、铜柱互连等。

5.2.3 学科交叉与应用拓展

集成电路学科将与人工智能深度融合,AI辅助设计(AI-EDA)将提升设计效率,AI芯片将优化计算架构;与量子信息交叉,量子芯片的研发需要集成电路技术支撑,同时量子计算可能颠覆传统芯片设计方法;与生物医学交叉,生物传感器芯片、植入式芯片将推动精准医疗发展。

应用场景将进一步拓展,物联网芯片实现万物互联,边缘计算芯片满足实时数据处理需求,太空芯片适应深空探测,核工业芯片耐受极端辐射。集成电路将渗透到更多领域,成为未来技术创新的核心支撑。

5.2.4 绿色低碳与可持续发展

低功耗设计成为学科重要方向,通过优化电路架构、采用新型器件、动态电压频率调节(DVFS)等技术,降低芯片功耗。芯片制造过程中的节能技术也将受到重视,如光刻设备的能效提升、废水废气处理技术优化。

回收利用技术将发展,废弃芯片中的贵金属与半导体材料可通过环保工艺回收,减少资源浪费。绿色低碳将成为集成电路产业的发展理念,贯穿设计、制造、使用全生命周期。

6.1 学科人才需求特点

集成电路学科人才需求呈现“高学历、跨学科、强实践”的特点。核心技术岗位如芯片设计工程师、制造工艺工程师,多要求硕士及以上学历;跨学科能力至关重要,需掌握电子工程、计算机科学、材料科学等多领域知识;实践能力直接影响工作成效,企业重视具有项目经验的人才。

人才缺口集中在先进制程工艺、EDA工具开发、高端芯片设计等领域。设计类人才需精通硬件描述语言与设计工具,制造类人才需熟悉工艺原理与设备操作,封装测试类人才需掌握封装技术与测试方法。

6.2 高校学科设置与课程体系

国内高校多在电子科学与技术、微电子科学与工程、集成电路设计与集成系统等专业开设集成电路相关课程。核心课程包括半导体物理、半导体器件、集成电路设计原理、数字电路设计、模拟电路设计、半导体制造技术、封装测试技术等。

实践课程是培养重点,包括芯片设计实践、光刻实验、刻蚀实验、封装实训等。高校通过建设集成电路实验室、与企业合作共建实习基地,提升学生实践能力。部分高校开设EDA工具开发、AI芯片设计等前沿课程,对接产业需求。

6.3 学习路径与能力提升

6.3.1 基础阶段(本科)

重点掌握数学、物理基础与专业核心知识。数学方面需学好线性代数、概率论与数理统计、复变函数,为电路分析与信号处理奠定基础;物理方面重点掌握固体物理、半导体物理;专业知识需吃透数字电路、模拟电路、半导体器件等核心课程。

积极参与学科竞赛与科研项目,如全国大学生集成电路设计竞赛,通过实践提升设计能力。学习Verilog/VHDL等硬件描述语言,掌握Cadence、Synopsys等主流设计工具的基本操作。

6.3.2 进阶阶段(硕士/博士)

确定研究方向,如数字芯片设计、模拟芯片设计、制造工艺、EDA工具开发等。硕士阶段侧重应用研究,完成特定芯片设计或工艺优化项目;博士阶段侧重理论创新,开展前沿技术研究,如新型器件结构、先进封装技术等。

发表高水平学术论文,参与国家级科研项目,与企业合作解决实际技术问题。深入学习领域前沿知识,如FinFET器件物理、EUV光刻技术、Chiplet集成技术等。培养独立科研能力与创新思维,为产业或科研机构输送高端人才。

6.3.3 职业阶段(企业/科研机构)

持续跟踪技术前沿,通过企业培训、行业会议、学术期刊等渠道更新知识。设计类人才需积累不同类型芯片的设计经验,提升时序优化与功耗控制能力;制造类人才需熟悉先进制程工艺,掌握设备调试与工艺改进方法;研发类人才需聚焦核心技术突破,提升自主创新能力。

培养团队协作能力与沟通能力,集成电路研发多为团队项目,需与设计、制造、测试等不同环节人员高效协作。树立终身学习理念,适应技术快速迭代的行业特点。

集成电路学科是信息技术发展的核心支撑,从手机、电脑到人工智能、航空航天,其应用无处不在。学科的发展不仅推动了技术进步,更重塑了产业格局与社会生活方式。在数字经济时代,集成电路学科的战略地位愈发凸显,是国家科技实力与核心竞争力的重要标志。

当前,学科面临物理极限、技术壁垒、人才缺口等多重挑战,但同时也迎来了AI、汽车电子、量子信息等新的发展机遇。通过材料、器件、工艺、封装等领域的协同创新,通过高校、企业、科研机构的紧密合作,集成电路学科必将突破瓶颈,开启新的发展阶段。

对于学习者与从业者而言,集成电路学科是充满机遇的领域。投身这一学科,不仅能实现个人职业价值,更能为国家核心技术自主可控贡献力量。在技术迭代与产业升级的浪潮中,集成电路学科将持续引领信息技术发展,书写科技进步的新篇章。