“原理图上不是都连在同一根线上吗?为什么放 TVS 的先后顺序会影响保护效果?”“如果因为板子空间不够、必须让信号先绕一下再到 TVS,到底是多严重的事?”

原理图是理想世界——几根线全都零电感、零电阻,看起来电视机天线都能接成超导体。

Layout 是真实物理世界——你画的每 1cm 走线,都是一个“缩小版电感器”,ESD 时候能气得你怀疑人生。

所以今天我们不讲玄学,只讲逻辑清晰、能让你立刻理解的真实物理——以及为什么多走那一点点线,ESD 性能直接“打骨折”。

一、问题本质:那些你以为不存在的“走线电感”

如上图,理想情况下,设计意图很简单:让静电放电的电流,优先流向 ESD/TVS,把能量吸掉,而不是侵入你的 MCU/FPGA 引脚。

但现实是——静电的速度远比你想象快,ESD 的频谱可以打到几十 MHz~几百 MHz。对于这种频率,哪怕短短几毫米的 PCB 线段,都会变成明显的电感。

也就是说,只要你拉长了 TVS 的路径,ESD 电流突然来了,它会发现:

“哎?那边的路线电感大,那我先往芯片里跑一口气吧。”然后你的芯片就可能提前退役。

二、走线电感到底有多大?算一下你就知道它不能忽略

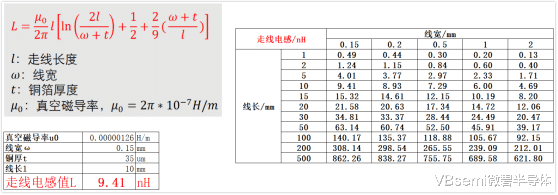

举个真实例子:线宽 6 mil、长度 1cm、1 oz 铜厚的走线 → 电感约 9.41 nH

光看 nH 可能没概念,代入阻抗计算式:

ZL=2πfLZ_L = 2\pi f LZL=2πfL

假设采用 ESD 典型频率点 50 MHz:

ZL≈2π×50MHz×9.41nH≈3ΩZ_L ≈ 2\pi \times 50 \text{MHz} \times 9.41\text{nH} ≈ 3 \OmegaZL≈2π×50MHz×9.41nH≈3Ω

没错,1cm 走线 ≈ 3Ω 高频阻抗。

3Ω 在 DC 看起来无所谓,但对 ESD 瞬态来说就像路中间突然出现的“减速带”:

电流过 TVS 变慢 → 更多电流冲向芯片 → 芯片承压上升

寄生电感会让 TVS 的“钳位电压”变高

但如果你的布局不好,信号线绕了点弯,带上了前面计算的 3Ω 阻抗,那么 ESD 电流 1A 流过电感,就会产生 3V 压降。

于是被保护芯片看到的电压不再是 10.5V,而是:

10.5V + 3V = 13.5V

很多 MCU 的容忍极限就 6V~12V 左右,这时候就危险了。

更夸张的是:

如果你不小心让线长成了 10cm……那电感约变成 140nH,50MHz 阻抗约 43Ω。

那么:

43Ω × 1A = 43V 压降

此时即便你用的是“高端 TVS”,也会被走线完全废掉。

四、那走线长一点一定没救吗?也不至于“死刑”,但你必须知道代价:

走线越长、越细 → 电感越大

电感越大 → TVS 越来不及“抢”电流

ESD 越容易窜入芯片内部结构

芯片越容易被击穿、性能漂移或寿命缩短

你可以采取一些补救措施,比如:

加宽走线降低电感

保持走线贴着参考地

为 TVS 单独规划最短接地回路

增加 RC 滤波或共模扼流

若空间超紧张,可考虑两级防护

但无论怎么补,原则永远不变:

TVS = 离接口越近越好,走线越短越好,接地回路越直接越好。五、总结(你必须记住的三句话)1. 原理图永远是理想世界;Layout 才是真实物理世界。2. PCB 走线电感是真实存在的,而且非常致命。3. 如果让信号“先走一段路再遇到 TVS”,ESD 的威力会被完整送到你的芯片上。用一句工程师圈的黑话总结就是:

“TVS 不要放远,放远了它就不叫 TVS,它叫摆设。”