圈内常有一句调侃:“做电路设计的,要么电路能‘跑’,要么人‘跑’,总得有一个在路上。” 本期就来复盘一个差点逼得工程师“提桶跑路”的棘手硬件故障案例,闲话少叙,直接看干货。

1. 故障复现【问题描述】 在对新产品的电池电压采样电路进行测试时,发现样机存在概率性的异常漏电现象:每五台样机中,就有一台会出现约 40uA 的额外静态电流。经过反复排查,最终将故障点锁定在 PMOS 管上,尝试更换新的 PMOS 后,故障现象暂时消失。

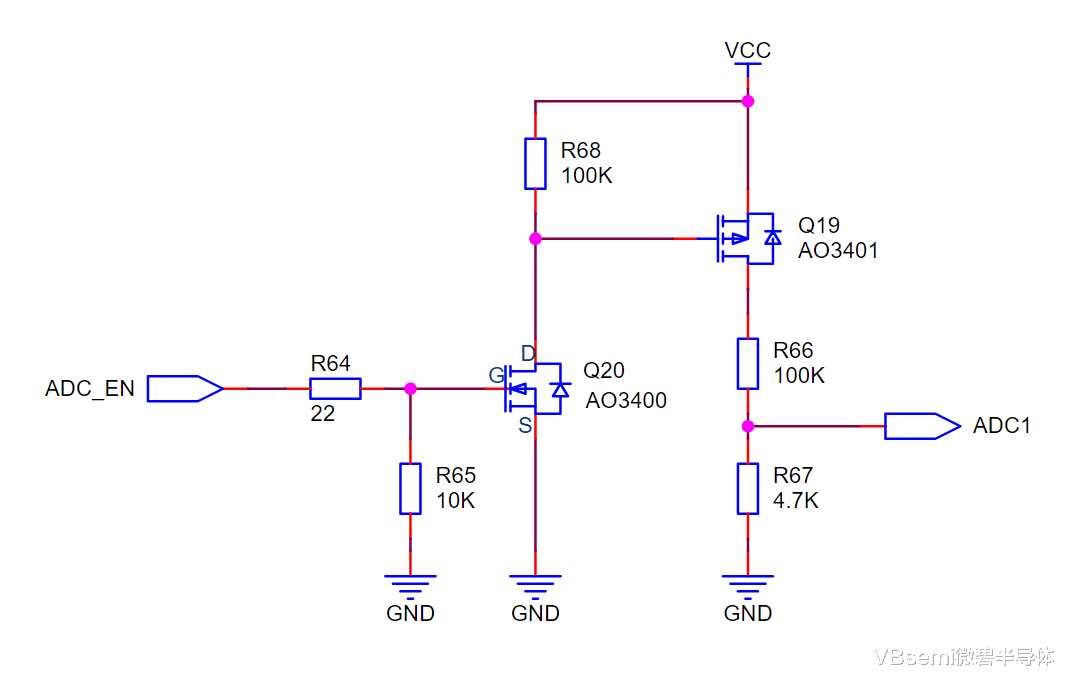

原始电路设计原理图如下:

【理论推演】从设计逻辑来看,该电路的工作机制如下:

当控制信号 拉高时,NMOS管(Q20)导通,进而拉低PMOS管(Q19)栅极使其导通,系统通过 网络采集输入电压(计算公式:ADC1≈V·CCx4.7K/104.7K)。

3. 深挖病灶

【原因定位】

虽然理论分析看似无懈可击,但现实情况是:在 Q19 本应完全截止的状态下,依然测出了 40uA 的漏电流。

到底哪里出了问题?经过仔细核对发现,该产品的供电端 连接的是 12V 蓄电池,其满电电压会远高于 12V。然而,该部分电路图是直接从之前 4.2V 锂电池项目中“移植”过来的。

问题就出在这个“直接拷贝”上:当 NMOS 导通瞬间,PMOS 的栅源电压VGS压差几乎等同于 (即大于 12V)。查阅我们使用的 PMOS 型号 AO3401 的数据手册可知,其VGS的绝对最大耐压值仅为士12V。

真相大白:由于电池电压超过了器件的承受极限,长期过压工作导致 PMOS 内部绝缘层受损(产生“内伤”),从而引发了莫名的漏电流。这也解释了为什么更换新管子后通过测试,但运行一段时间又出问题。

4. 整改措施

针对上述分析,提出以下三种解决方案:

方案一:优化驱动电路 在 PMOS 栅极前增加电阻分压网络,强行降低VGS的压差,使其工作在安全范围内。修改后的电路拓扑如下:

5. 避坑总结

设计电路时,切勿盲目照搬旧方案。务必仔细校核 MOS 管的VGS(栅源电压)与VDS(漏源电压)耐压参数,确保其覆盖实际工作电压范围,切莫随心所欲,因小失大。