在电力电子设计中,我们经常遇到一个有趣的现象:工程师们往往绞尽脑汁去加速MOS管的“关断”过程,相比之下,对“开通”速度的要求似乎没有那么苛刻 。这背后的深层原因究竟是什么?

一、 典型的加速关断电路设计首先,我们来看一个经典的MOS管驱动拓扑结构:

在这个电路中,MOS管的开关速度本质上取决于栅极电容充放电的快慢:栅极回路中的串联电阻阻值越大,充放电耗时越长,开关动作就越迟缓 。

为了实现“快关”,电路中引入了一个二极管 D和一个辅助电阻 Rs_off(有时直接短路,即 0欧姆) 其工作机制如下:

开通阶段: 驱动信号 Vg_drive 输出高电平。此时,二极管 D处于反向截止状态,并不导通。驱动电流完全流经 Rs_on 为栅极充电。换言之,该二极管支路的存在并不影响开通速度。

关断阶段: 驱动信号 Vg_drive拉低至 GND。此时,栅极电压高于驱动端,二极管 D导通。栅极电荷通过 Rs_on和 Rs_off 两条路径同时泄放。根据并联电阻原理,等效电阻 Req= Rs_off// Rs_on必然小于单独的 Rs_on。阻值减小,放电加快,从而实现了“快速关断” 。

二、 为什么要刻意“加速”关断?这就引出了核心问题:为什么我们需要专门增加外围器件来加速关断?

根本原因在于:即使栅极充、放电回路的电阻完全相同,MOS管天然的“关断”耗时也要比“开通”耗时更长 。

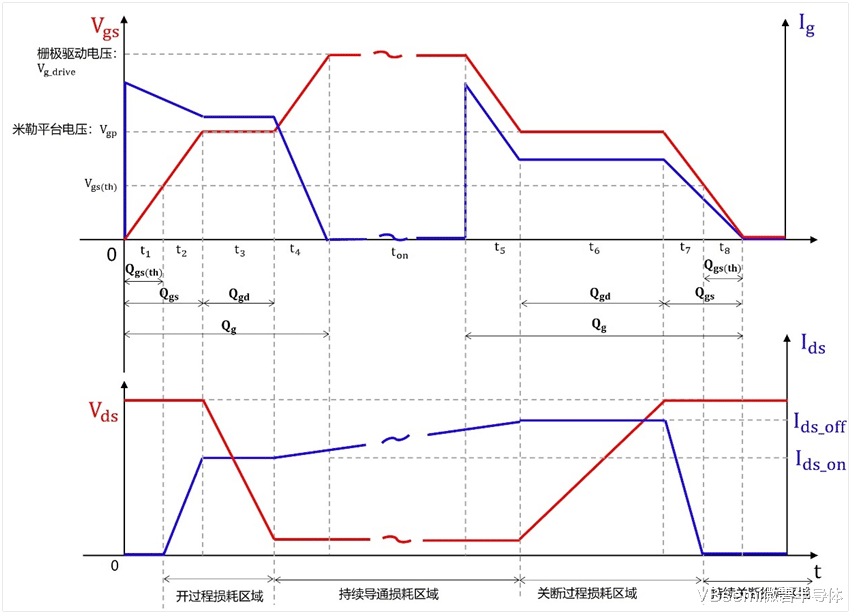

为了理解这一点,我们需要分析MOS管的损耗区间。开通损耗主要发生在 t2 和 t3 阶段,而关断损耗则集中在 t6和 t7 阶段。

三、 物理层面的深度剖析

我们将开通与关断过程拆解为两组对应的物理过程进行对比,就能发现其中的不对称性。

t2阶段 vs t7 阶段:RC充放电曲线的差异

这两个阶段互为逆过程:

t2(开通): 栅极电压从门限电压 Vgs(th) 上升至米勒平台电压 Vgp12。

t7 (关断): 栅极电压从米勒平台电压 V_gp 下降回门限电压 V_gs(th)。

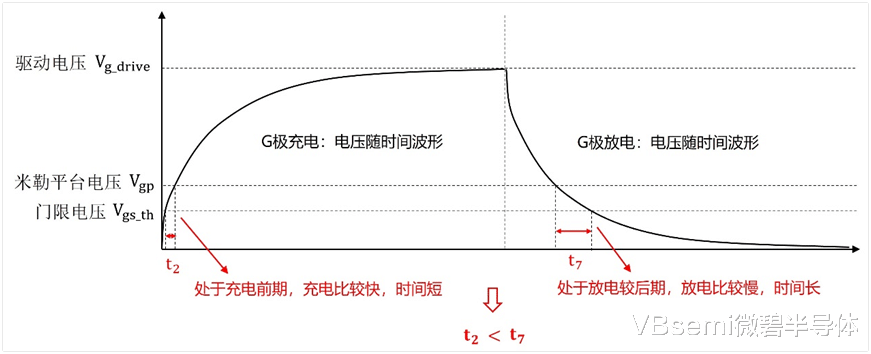

虽然直觉上认为时间应该相等,但实际上并非如此 14。我们需要引入RC电路模型来解释。

MOS管开通和关断的电路模型对比如下图:

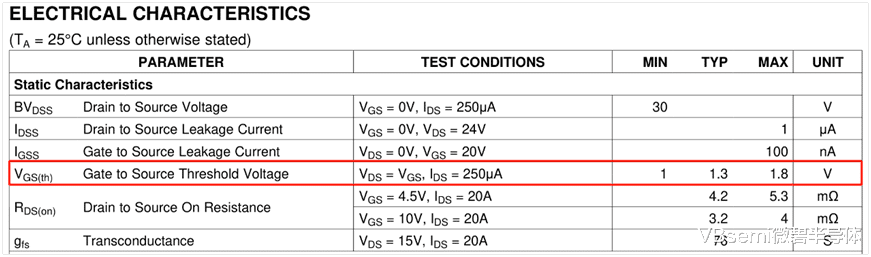

可以看到,充电时,电压在起始阶段上升极快;而放电时,电压在末尾阶段下降极慢。关键在于具体的电压数值分布:通常 MOS 管的 Vgs (th) 约为 1.3V,米勒平台 Vgp 约为 2.5V,这两个值都比较低。而驱动电压 Vg_drive 通常高达 10V 或以上。

在开通(t2)时:我们是从 0V 开始充电。由于目标 Vgp (2.5V) 距离起点 (0V) 很近,且远低于终点 (10V),这段过程处于充电曲线最陡峭、最快速的前端区域。

在关断(t7)时:我们是从 10V 开始放电。目标是将电压降至 Vgp (2.5V) 甚至更低。由于 2.5V 距离起点 (10V) 很远,已经进入了放电曲线的尾部平缓区域,导致放电速率显著变慢。

结论:从波形上可以直观地看到,t2 的耗时必然小于 t7。

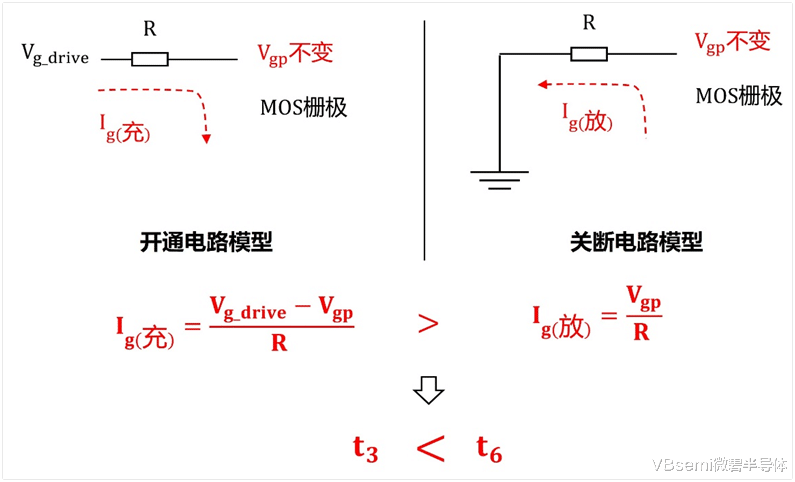

t3 阶段 vs t6 阶段:驱动电流的差异

这两个阶段对应的是米勒平台期:

t3 (开通):维持在 Vgp 对应的时间。

t6 (关断):维持在 Vgp 对应的时间。

在此期间,栅极电压保持恒定,处理的电荷量均为米勒电荷 Qgd。

此时决定速度的是回路电流的大小:

开通电流:Ig (on) = (Vg_drive - Vgp) / R

关断电流:Ig (off) = Vgp / R

由于 Vg_drive (如 10V) 远大于 Vgp (如 2.5V),分子上的压差 (10 - 2.5) 显然大于单独的 2.5。因此,开通时的驱动电流远大于关断时的放电电流。

结论:电荷量相同,电流越大时间越短,所以 t3 耗时小于 t6。

数据验证与总结

数据清晰地佐证了上述理论:

t2 (18ns) 远快于 t7 (88.6ns)

t3 (29.8ns) 远快于 t6 (104.5ns)

总结:之所以 MOS 管的关断过程显得 “拖泥带水”,是因为其门限电压 Vgs_th 和米勒平台电压 Vgp 相对于驱动电压而言非常低(通常仅 1~3V)。这使得开通过程利用了 RC 曲线最陡峭的 “快速区” 和较大的压差电流,而关断过程则不得不面对 RC 曲线平缓的 “慢速区” 和较小的泄放电流。为了平衡这种天然的不对称性,在驱动电路中增加二极管加速关断就成为了必不可少的标准设计。